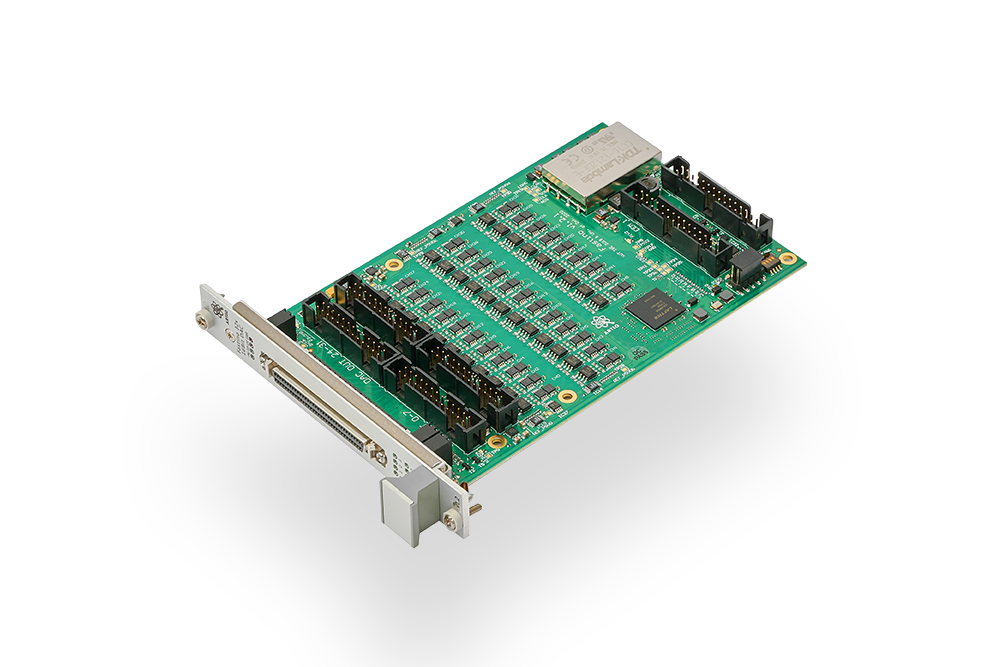

Fastino is a faster DAC than Zotino, meant for more demanding applications like a servo with ADC input (in combination with Sampler) and voltage output.

Technical Parameters

Specification

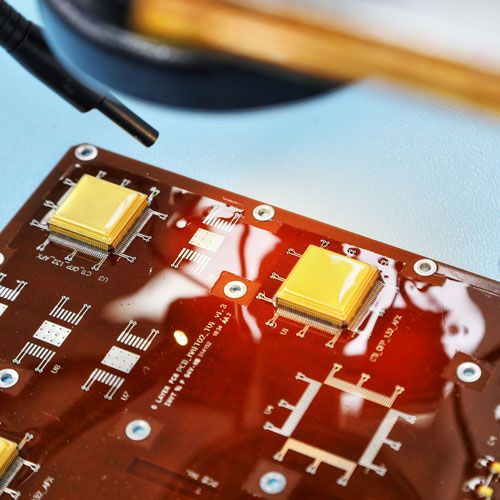

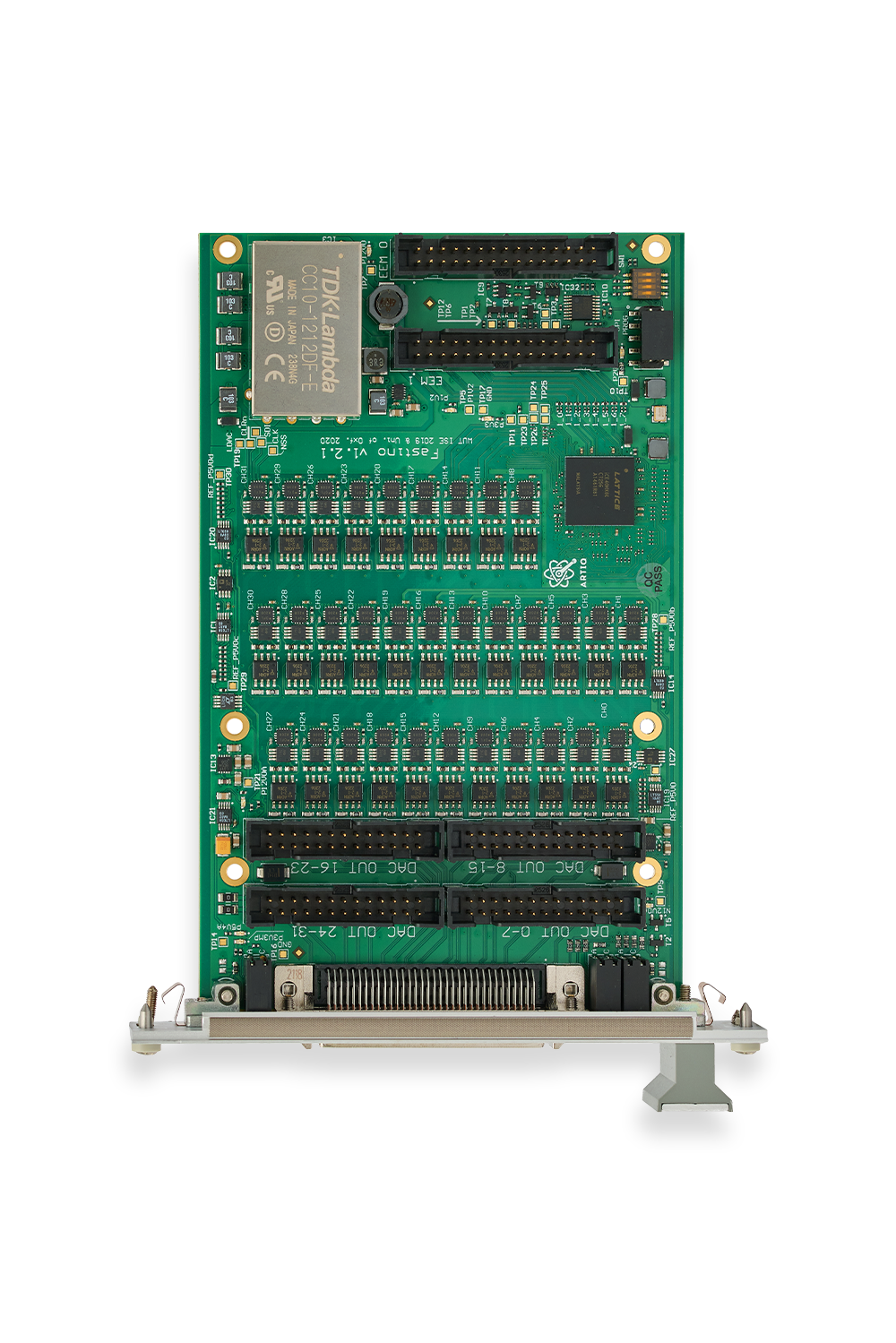

- 32 channels, 2.55 MS/s simultaneous, 16 bit resolution, 1 Gb/s aggregate, AD5542ABCPZ DAC with 1μs settling time,

- Interface: dual EEM

- Data/clock/LDAC masking on channels for intervals to suppress digital crosstalk, no contention between configuration and data.

- Update rate on DAC masking: ~1 µs

Components

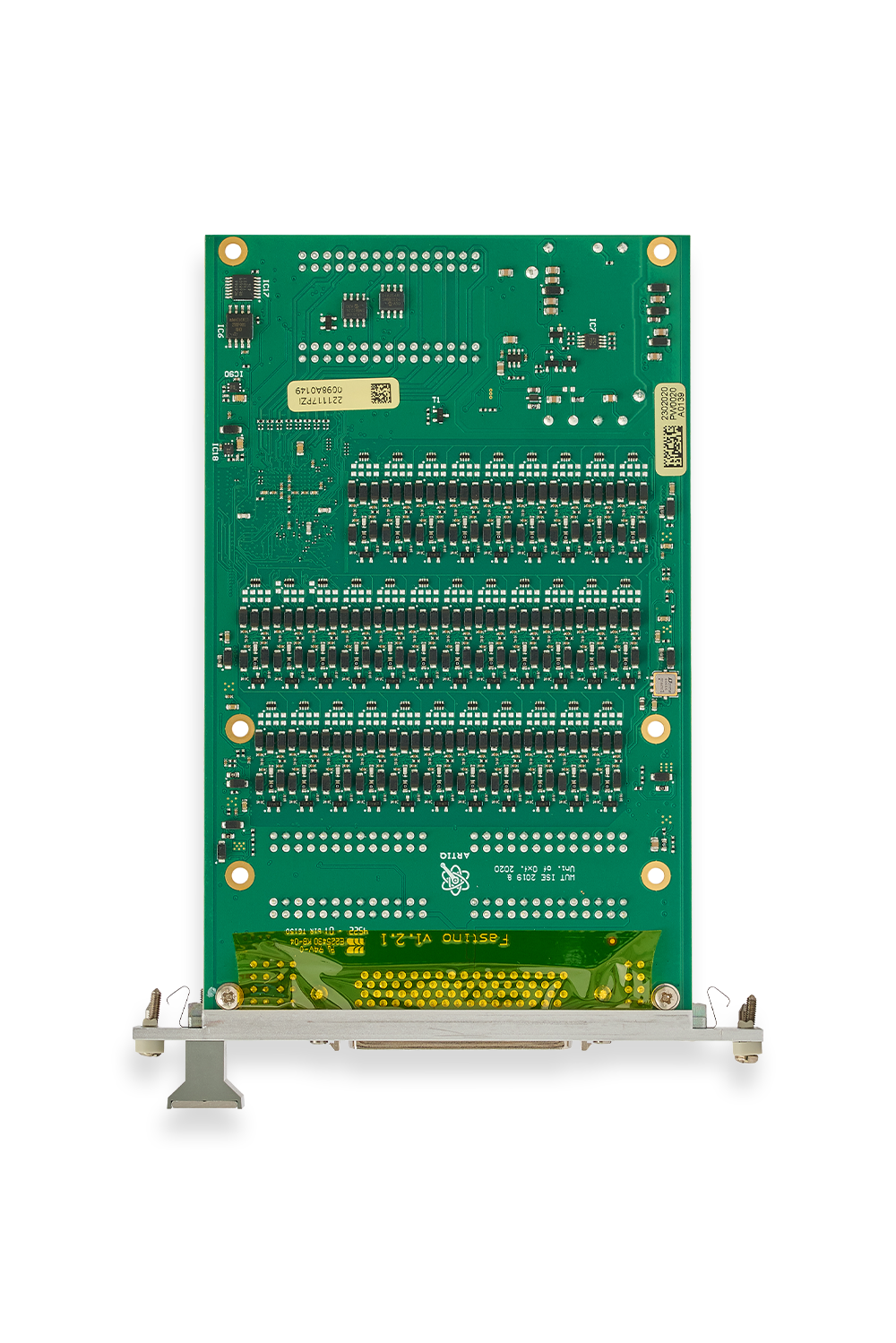

- PHY layer of framed data at 1 Gb/s over multilane LVDS with slower return channel (1 EEM), serialization/deserialization/framing.

- DAC interface: PLL for SPI bitclock, sample clocking, CLR, LDAC.

- Out-of-band configuration layer: configuration, LEDs, clocking, channel masking.

- RTIO channel design baseline: 32×16 bit = 512-bit DAC data events on existing kernel/DMA/DRTIO infrastructure

- ARTIQ core device API.

Applications

This module can be used for building control and measurement systems for optical and quantum physics experiments and quantum technologies development. In particular, the Sinara ecosystem is tailored to the needs of working with trapped ions and cold atoms. Compatible with ARTIQ software.

Download

More technical information: https://github.com/sinara-hw/Fastino/wiki

Support

We offer electronics engineering consultancy services related to Sinara hardware, including: custom modifications of hardware, custom firmware and gateware modifications, system design, integration and testing.

Order now

Please contact us concerning details of your order and any requirements you may have towards our equipment. All shipping details will be set up as well.

Subscribe to receive latest news:

Subscribe to receive latest news: